### Features

- Fully Autonomous DSP System

- 16-bit Fixed-point OakDSPCore<sup>®</sup>

- 24K x 16 of Uploadable Program RAM

- 16K x 16 of Data RAM

- 2K x 16 of X-RAM

- 2K x 16 of Y-RAM

- X-RAM and Y-RAM Accessible within the Same Cycle

- JTAG Interface Available on AT75C220 and AT75C320

- On-chip Emulation Module

- Flexible Codec Interface

- Communication with External Processor through Dual-port Mailbox

# Description

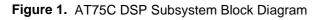

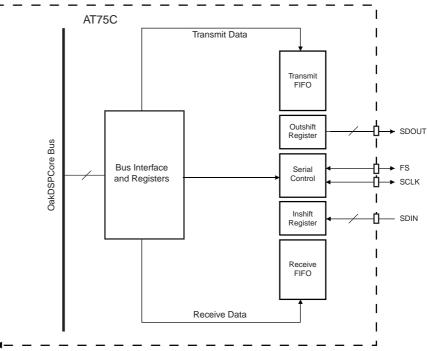

The AT75C DSP subsystem is an autonomous DSP-based computation block that coexists on-chip with other processors and functions. It is built around a 16-bit, fixedpoint, industry-standard OakDSPCore. Additionally, the DSP subsystem embeds all elements necessary to run complex DSP algorithms independently without any external resources.

The self-contained subsystem contains the OakDSPCore itself, program memory, data memory, an on-chip emulation module and a flexible codec interface. These resources allow the subsystem to run complex DSP routines, such as V.34 modem emulation or state-of-the-art voice compression.

The codec interface permits connection of any external industry-standard codec device, allowing the DSP subsystem to handle directly external analog signals such as telephone line or handset signals.

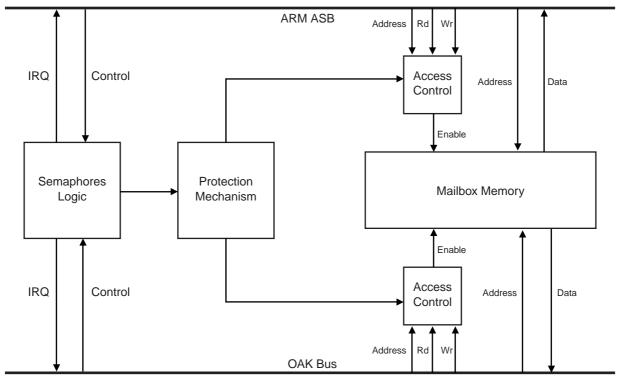

Communication between the DSP subsystem and the on-chip ARM7TDMI<sup>™</sup> core is achieved through a semaphore-operated dual-port mailbox.

Smart Internet Appliance Processor (SIAP<sup>™</sup>)

# AT75C DSP Subsystem

Rev. 1368C-INTAP-08/02

### Architectural Overview

### **Processing Unit**

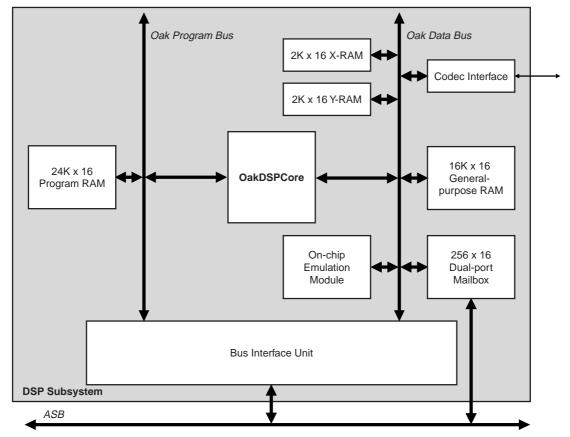

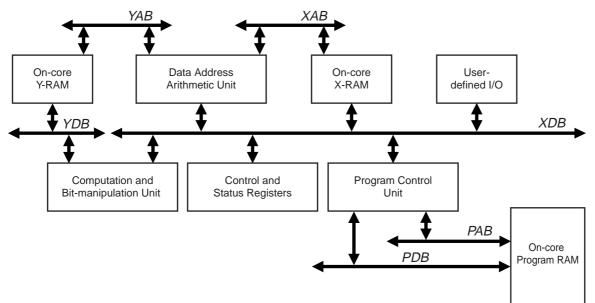

A block diagram of the OakDSPCore architecture is shown in Figure 2.

The major components of the OakDSPCore are:

- Computation and Bit-manipulation Unit (CBU) Accumulators (A0, A1, B0, B1) Saturation Logic Arithmetic and Logical Unit (ALU)

- Bit-field Operations (BFO)

- Shift Value Register (SV)

- Barrel Shifter

- Exponent Logic (EXP)

- Multiplier

- Input Registers (X, Y)

- Output Register (P)

- Output Shifter

- Data Address Arithmetic Unit (DAAU)

DAAU Registers (R0...R5)

DAAU Configuration Registers (CFGI, CFGJ)

Software Stack Pointer (SP)

Base Register (RB)

Alternative bank of registers (R0B, R1B, R4B, CFGIB)

Minimal/Maximal Pointer Register (MIXP)

- Data buses (XDB, YDB, PDB)

- Address buses (XAB, YAB, PAB)

- Program Control Unit (PCU)

Loop Counter (LC)

Internal Repeat Counter (REPC)

- Memories

On-core Data Memories (X-RAM, Y-RAM)

Program Memory

- Control Registers Status Registers (ST0, ST1, ST2) Interrupt Context Switching Register (shadow and swap) Internal Configuration Register (ICR) Data Value Match Register (DVM)

- User-defined I/Os

### **Bus Architecture**

#### Data Buses

Data is transferred via the X-data bus (XDB) and the program data bus (PDB), 16-bit bidirectional buses, and the Y-data bus (YDB), a 16-bit unidirectional bus. The XDB is the main data bus, where most of the data transfers occur. Data transfer between the Ydata memory (Y-RAM) and the multiplier (Y-register) occurs over the YDB when a multiply instruction uses two data memory locations simultaneously. Instruction word fetches take place in parallel over PDB.

The bus structure supports the following movements:

- Register to register

- Register to memory

- Memory to register

- Program to data

- Program to register

- Data to program

The bus structure can transfer up to two 16-bit words within one cycle.

#### Address Buses

Addresses are specified for the on-core X- and Y-RAM on the 16-bit unidirectional Xaddress bus (XAB) and the 11-bit unidirectional Y-address bus (YAB). Program memory addresses are specified on the 16-bit unidirectional program address bus (PAB).

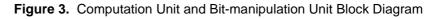

### **Computation and Bit-manipulation Unit**

The computation and bit-manipulation unit (CBU) contains two main units, the computation unit (CU) and the bit-manipulation unit (BMU). The saturation unit is shared by the CU and the BMU units. A detailed block diagram of the computation and bit-manipulation unit is shown below in Figure 3.

**Computation Unit** The computation unit (CU) consists of the multiplier unit, the ALU and two 36-bit accu-

**Multiplier Unit**

mulator registers (A0 and A1), as shown in Figure 3.

The multiplier unit consists of a 16-by-16 to 32-bit parallel 2's complement, single-cycle, non-pipelined multiplier, two 16-bit input registers (X and Y), a 32-bit output register (P), and a product output shifter. The multiplier performs signed-by-signed, signed-byunsigned or unsigned-by-unsigned multiplication. Together with the ALU, the OakDSP-Core can perform a single-cycle multiply-accumulate (MAC) instruction. The register P is updated only after a multiply instruction and not after a change in the input registers.

The X- and Y-registers are read or written via the XDB, and the Y-register is written via YDB, as 16-bit operands. The 16-bit Most Significant Portion (MSP) of the P register, PH, can be written by the XDB as an operand. This enables a single-cycle restore of PH during interrupt service routine. The complete 32-bit P register, sign-extended into 36 bits and shifted by the output shifter, can be used only by the ALU and can be moved only to the A0 and A1 accumulators.

The X- and Y-registers can be also used as general-purpose temporary data registers.

Product Output ShifterThe register P is sign-extended into 36 bits and then shifted. In addition to passing the<br/>data unshifted, the output shifter is capable of shifting the data from the register P into<br/>the ALU unit by one bit to the right or by one and two bits to the left. In right shift, the<br/>sign is extended, whereas in left shift, a zero is appended to the LSBs. Shift operation is<br/>controlled by two bits (PS) in the status register ST1. The shifter also includes alignment<br/>(a 16-bit right shift) for supporting double-precision multiplication.

Double-precision Multiplication The OakDSPCore supports double-precision multiplication by several multiplication instructions and by alignment option of the register P. The register P can be aligned (shifting 16 bits to the right) before accumulating the partial multiplication results, in multiply-accumulate instructions (MAA and MAASU instructions). An example of different multiplication operations is in the multiplication of 32-bit by 16-bit fractional numbers, where two multiplication operations are needed: multiplying the 16-bit number with the lower or upper portion of a 32-bit (double-precision) number. The signed-by-unsigned operation is used to multiply or multiply-accumulate the 16-bit signed number with the lower, unsigned portion of the 32-bit number. The signed-by-signed operation is used to multiply the 16-bit signed number with the upper, signed portion of the 32-bit number. While the signed-by-signed operation is executed, it is recommended to accumulate the aligned (using MAA instruction) result of the previous signed-by-unsigned operation. For the multiplication of two double-precision (32-bit) numbers, the unsigned operation can be used. If this operation requires a 64-bit result, the unsigned-by-unsigned operation should be used. For details, on the various multiply instructions (MPY, MPYSU, MACUS, MACUU, MAA, MAASU, MSU and MPYI), refer to "Instruction Set" on page 31.

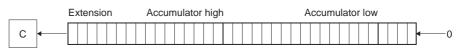

Ax-accumulators Each Ax-accumulator is organized as two regular 16-bit registers (A0H, A0L, A1H and A1L) and a 4-bit extension nibble (A0E and A1E). The two portions of each accumulator can be accessed as any other 16-bit data register and can be used as 16-bit source or destination registers in all relevant instructions. The Ax-accumulators can serve as the source operand and the destination operand of the ALU, barrel shifter and exponent units. The extension nibbles of the A0 and A1 accumulators can be swapped with the Bx-accumulators in a single cycle. Saturation arithmetic is provided to selectively limit overflow from the high portion of an accumulator to the extension bits when performing a move instruction from one of the accumulators through the XDB, or when using the LIM instruction, which performs saturation on the 36-bit accumulator. For more details, refer to "Saturation" on page 12.

Registers AxH and AxL can also be used as general-purpose, temporary 16-bit data registers.

Extension NibblesExtension nibbles A0E and A1E offer protection against 32-bit overflows. When the<br/>result of an ALU output crosses bit 31, it sets the extension flag (E) in ST0, representing<br/>crosses of the MSB in AxH. Up to 15 overflows or underflows are possible using the<br/>extension nibble, after which the sign is lost beyond the MSB of the ALU output and/or<br/>beyond the MSB of the extension nibble, setting the overflow flag (V) in ST0, and also<br/>latching the Limit flag (L) in ST0. Refer to "Status Registers" on page 23 for more detail.

Sign ExtensionSign extension of the 36-bit Ax-accumulators is provided when the Ax or AxH is written<br/>with a smaller size operand. This occurs when these registers are written from XDB,<br/>from the ALU or from the exponent unit in certain CBU operations. Sign extension can<br/>be suppressed by specific instructions. For details, refer to "Instruction Set" on page 31.

Loading of Ax-accumulators AxL is cleared while loading data into AxH, and AxH is cleared while loading AxL. Loading a full 32-bit value is accomplished via the ADDL or ADDH instructions (refer to

|  |  | R |

|--|--|---|

"Instruction Set" on page 31). The full 36-bit accumulators can also be loaded using the shift instructions or with another 36-bit accumulator in a single cycle using the SWAP instruction. For details, refer to the sections "Swapping the Accumulators" on page 13 and "Instruction Set" on page 31.

Arithmetic and Logic Unit The Arithmetic and Logic Unit (ALU) performs all arithmetic and logical operations on data operands. It is a 36-bit, single-cycle, non-pipelined ALU.

The ALU receives one operand from Ax (x = 0,1), and another operand from either the output shifter of the multiplier, the XDB (through bus alignment logic), or from Ax. The source operands can be 8, 16 or 36 bits. Operations between the two Ax-accumulators are also possible. The source and destination Ax-accumulator of an ALU instruction is always the same. The XDB input is used for transferring one of the register's contents, an immediate operand or the contents of a data memory location addressed in direct memory addressing mode, indirect addressing mode, index addressing mode or pointed to by the stack pointer, as a source operand. The ALU results are stored in one of the Ax-accumulators or transferred through the XDB to one of the registers or to a data memory location. The latter is used for addition, subtraction and compare operations between a 16-bit immediate operand and a data memory location or one of the registers, without effecting the accumulators, in two cycles. The add and subtract are part of the read-modify-write instructions. Refer to ADDV, SUBV, CMPV instructions in "Instruction Set" on page 31. A bit-field operation (BFO) unit is attached to the ALU and described in detail in "Bit-field Operations".

The ALU can perform positive or negative accumulate, add, subtract, compare, logical and several other operations, most of them in a single cycle. It uses 2's complement arithmetic.

Unless otherwise specified, in all operations between an 8-bit or 16-bit operand and a 36-bit Ax, the 16-bit operand will be regarded as the LSP of a 36-bit operand with sign extension for arithmetic operations and zero extension for logical operations. The ADDH, SUBH, ADDL and SUBL instructions are used when this convention is not adequate in arithmetic operations. For details, refer to these instructions in "Instruction Set" on page 31.

The flags are affected as a result of the ALU output, as well as a result of the BFO or the barrel shifter operation. In most of the instructions where the ALU result is transferred to one of the Ax-accumulators, the flags represent the Ax-accumulator status.

Rounding Rounding (by adding 0x8000 to the LSP of the accumulator) can be performed by special instructions, in a single cycle or in parallel to other operations. Refer to MOVR and MODA instructions in "Instruction Set" on page 31.

Division Step A single-cycle division step is supported. For details, refer to the DIVS instruction in "Instruction Set" on page 31.

Logical Operations The logical operations performed by the ALU are AND, OR, and XOR. All logical operations are 36 bits wide. 16-bit operands are zero extended when used in logical operations. The source and destination Ax-accumulator of these instructions is always the same. Operations between the two Ax-accumulators are also possible. For details, refer to AND, OR and XOR instructions in "Instruction Set" on page 31.

Other logical operations are set, reset, change and test, executed on one of the registers or on data memory contents. Refer to "Bit-field Operations" on page 11.

Maximum/Minimum Operations A single-cycle maximum/minimum operation is available, with pointer latching and modification. One of the Ax-accumulators, defined in the instruction, holds the maximal value in a MAX instruction, or the minimal value in a MIN instruction. In one cycle the two accumulators are compared and when a new maximal or minimal number is found, this value is copied to the above-defined accumulator. In the same instruction, the register R0 can be used, for example, as a buffer pointer. This register can be post-modified according to the specified mode in the instruction. When the new maximal or minimal number is found, the R0 pointer is also latched into the 16-bit dedicated minimum/maximum pointer latching (MIXP) register - one of the DAAU registers. The maximum operation can also be performed directly on a data memory location pointed to by the register R0 (MAXD instruction), saving the maximal number in the defined Ax-accumulator and latching the R0 value into MIXP in a single cycle. For more details, refer to MAX, MAXD and MIN instructions in "Instruction Set" on page 31. For more details on registers R0 and MIXP, refer to "Data Address Arithmetic Unit (DAAU)" on page 14. When finding the maximum/minimum value, a few buffer elements can have the same value. The accumulator will save the same value; the latched pointer, however, depends on the condition used in the instruction. In finding the maximum value, the pointer of the first element or the last element will be latched, using greater than (>), or greater-thanor-equal to (≥) conditions, respectively. In finding the minimum value, the pointer of the first element or the last element will be latched, using less than (<), or less- than-orequal to ( $\leq$ ) conditions, respectively. All these cases are supported by the MAX, MAXD and MIN instructions. **Bit-manipulation Unit** The bit-manipulation unit (BMU) consists of a full 36-bit barrel shifter, an exponent unit (EXP), a bit-field operation unit (BFO), two 36-bit accumulator registers (B0 and B1), and the shift value (SV) register. Refer to Figure 3 on page 6. **Barrel Shifter** The barrel shifter performs arithmetic shift, logical shift and rotate operations. It is a 36bit left and right, single-cycle, non-pipelined barrel shifter. The barrel shifter receives the source operand from either one of the four accumulators (A0, A1, B0, B1) or from the XDB (through bus alignment logic). The XDB input is used for transferring the contents of one of the registers or a data memory location, addressed in direct memory addressing mode or in indirect addressing mode. The source operands may be 16 or 36 bits. The destination of the shifted value is one of the four accumulators. The amount of shifts is determined by a constant embedded in the instruction opcode or by a value in the SV register.

The flags are effected as a result of the barrel shifter output, as well as a result of the ALU and BFO outputs. When this result is transferred into one of the accumulators, the flags represent the accumulator status.

Shifting Operations A few options of shifting are available using the barrel shifter, all of them performed in a single cycle. Each of the four accumulators can be shifted according to a 6-bit signed number representing +31, -32 shifts (shift left is a positive number, while shift right is a negative number) embedded in the instruction opcode, into each of the four accumulators. The accumulators can also be shifted conditionally, according to the SV register content. In this case the accumulators can be shifted by +36, -36. This supports calculating the amount of shifts at run-time as, for example, in normalization operations. Refer to "Normalization" on page 11.

The source and the destination accumulators can be the same or different. If the accumulators are different, the source accumulator is unaffected. For details, refer to SHFC and SHFI instructions in "Instruction Set" on page 31.

In addition to the conditional shifting operations performed when the accumulators are shifted according to the SV register (by +36, -36), the shift and rotate operations included in the MODA and MODB instructions are also performed conditionally. MODA and MODB include:

- 1-bit right and left arithmetic shift and rotate

- 4-bit right and left arithmetic shift

For details, refer to MODA and MODB instructions in "Instruction Set" on page 31.

Arithmetic left shift and logical left shift perform the same operation, filling the LSBs with zeros. During an arithmetic right shift, the MSBs are sign extended and during a logical right shift, the MSBs are filled with zeros. Whether the shift mode is arithmetic or logic is determined according to the Status mode bit (S) in the register ST2. It affects all shift instructions.

#### Figure 5. Logical Shift Right

#### Figure 6. Logical Shift Left

| Move and Shift Operations | The four accumulators can be loaded by a shifted value, according to the SV register content, in a single cycle. The accumulators can be loaded from one of the registers or from a data memory location, addressed in direct addressing mode or indirect addressing mode, according to the SV shift value. The shifting capability is +36, -36, (shift left is a positive number, while shift right is a negative number). The accumulators can also be loaded by one of the DAAU registers (Rn registers), shifted according to a constant embedded in the instruction opcode. The shifting capability in this case is 15 to -16. Whether arithmetic shift mode or logic shift mode is selected is determined by the Status mode bit (S) in the register ST2. Refer to MOVS and MOVSI instructions in "Instruction Set" on page 31. |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | The register content or a data memory location content can be moved and shifted according to the SV shift value into one of the four accumulators in a single cycle. One of the four accumulators can also be loaded by a shifted value of the DAAU registers (Rn registers), according to a constant embedded in the instruction opcode, also in a single cycle. The shifting capability in this case is 16 to -15. Refer to "Instruction Set" on page 31 for MOVS and MOVSI instructions.                                                                                                                                                                                                                                                                                                                                           |

| Exponent Unit             | The exponent unit (EXP) performs exponent evaluation of one of the four accumulators, of a data memory location or of one of the registers. The result of this operation is a signed 6-bit value sign-extended into 16 bits and transferred into the shift value register (SV). Optionally, it can also be transferred, sign-extended into 36 bits, into one of the Ax-accumulators. The source operand is unaffected by this calculation. The source                                                                                                                                                                                                                                                                                                                                                                                 |

# 10 AT75C DSP Subsystem

operand can be 36 bits when it is one of the accumulators or 16 bits when it is a data memory location or one of the registers.

The algorithm for determining the exponent result for a 36-bit number is as follows: Let N be the number of the sign bits (i.e., the number of MSBs equal to bit 36) found in the evaluated number. This means that the exponent is evaluated with respect to bit 32. For a 16-bit operand, the 16 bits are regarded as bits 16 31, sign-extended into bits 32 to 35 and then treated as a 36-bit operand. Therefore, in this case, the exponent result is always greater than or equal to zero. For examples, refer to Table 1 on page 11.

A negative result represents a number for which the extension bits are not identical. The value of this negative result stands for how many right shifts should be executed in order to normalize the number, i.e., bit 31 (representing the sign) and bit 30 (representing part of the magnitude) will be different. A positive result represents an un-normalized number for which at least the four extension bits and the sign bits are the same. When evaluating the exponent value of one of the accumulators, the positive number is the amount of left shifts that should be executed in order to normalize the source operand. An exponent result equal to zero represents a normalized number.

Examples including an application in a normalization operation can be found in Table 1 below.

| Evaluated Number<br>[35:] | N | Exponent Result N-5   | Normalized Number<br>[35:] |

|---------------------------|---|-----------------------|----------------------------|

| 0000 0000101              | 8 | 3 (shift left by 3)   | 0000 0101                  |

| 1100 10101                | 2 | -3 (shift right by 3) | 1111                       |

| 0000 0111000              | 5 | 0 (no shift)          | 0000 0111000               |

Table 1.

Normalization Operation Examples

Full normalization can be achieved in two cycles using the EXP instruction followed by a shift instruction. For more details, refer to the section below on normalization, or to the EXP, SHFC and MOVS instructions in "Instruction Set" on page 31.

The exponent unit can also be used in floating-point calculations, where it is useful to transfer the exponent result into both the SV register and one of the Ax-accumulators.

Two techniques for normalization are provided. Using the first technique, normalization can be done by two cycles using two instructions. The first instruction evaluates the exponent value of one of the registers including the accumulators, or the value of a data memory location. The second instruction is shifting the evaluated number according to the exponent result stored at SV register. The second technique is using a normalization

Normalization

Bit-field Operations

The bit-field operation unit (BFO) is used for set, reset, change or test a set of up to 16 bits within a data memory location or within one of the registers. The data memory location can be addressed using a direct memory or an indirect address. The SET, RST and CHNG instructions are read-modify-write and require two cycles and two words. The 16-bit immediate mask value is embedded in the instruction opcode. Various testing instructions can be used. Testing for zeros (TST0) or for ones (TST1), of up to 16 bits in a single cycle, can be achieved when the mask is in one of the AxL or in two cycles when the mask value is embedded in the instruction opcode.

step (NORM instruction). For details, refer to "Instruction Set" on page 31.

Testing instruction (TSTB) for a specific bit, 1 out of 16, in a data memory location or in one of the registers in a single cycle, is also available. For details, refer to SET, RST, CHNG, TST0, TST1, TSTB instructions in the "Instruction Set" on page 31.

|                         | The bit-field operation unit (BFO) is attached to the ALU. Flags are affected as a result of the bit-field operations as well as a result of the ALU and the barrel shifter operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

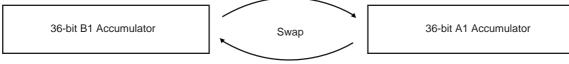

| Bx-accumulators         | Each Bx-accumulator is organized as two regular 16-bit registers (B0H, B0L, B1H and B1L) and a 4-bit extension nibble. The two portions of each accumulator can be accessed as 16-bit data registers using the XDB bus and can be used as 16-bit source or destination data registers in relevant instructions. The Bx-accumulators can be swapped with the Ax-accumulators in a single cycle. Saturation arithmetic is provided to selectively limit overflow from the high portion of an accumulator to the extension bits when performing a move instruction from one of the accumulators through the XDB. For more details, refer to "Saturation" on page 12. |

|                         | Each of the Bx-accumulators can be a source operand of the exponent unit and can be a source operand or a destination operand of the barrel shifter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Extension Nibbles       | Extension nibbles of B0 and B1 offer protection against 32-bit overflows. When the result of the barrel shifter crosses bit 31, it sets the extension flag (E) in ST0, representing crosses of the MSB at BxH. When the sign is lost beyond the MSB of the barrel shifter and/or beyond the MSB of the extension nibble, the overflow flag (V) in ST0 is set and latched in the Limit flag (L) in ST0. Refer to "Status Registers" on page 23 for more details. The extension bits can be accessed with the aid of a single-cycle shift instruction or by swapping to the Ax-accumulator.                                                                         |

| Sign Extension          | Sign extension of the 36-bit Bx-accumulators is provided when the Bx or BxH is written with a smaller size operand. This occurs when these registers are written from XDB or from the barrel shifter in shift operations.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Loading Bx-accumulators | BxL is cleared while loading data into BxH and BxH is cleared while loading BxL. The full 36-bit accumulator can be loaded in a single cycle, using the shift instructions or by another 36-bit accumulator, using the SWAP instruction (refer to "Swapping the Accumulators" on page 13 and "Instruction Set" on page 31).                                                                                                                                                                                                                                                                                                                                       |

| Shift Value Register    | The shift value (SV) register is a 16-bit register used for shifting operations and expo-<br>nent calculation. In shift operations it determines the amount of shifts and therefore<br>enables calculating the amount of shifts at run-time. The exponent result is transferred<br>to the SV register. This register can be used for full normalization by serving as the des-<br>tination of the exponent calculation and as the control for the shift (see "Normalization"<br>on page 11 and "Instruction Set" on page 31).                                                                                                                                     |

|                         | The SV register can also be used as a general-purpose temporary data register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Saturation              | Saturation arithmetic is provided to selectively limit overflow from the high portion of an accumulator to the extension bits. Saturation is performed when moving from the high portion or low portion of one of the accumulators through the XDB, or when using the LIM instruction, which performs saturation on the 36-bit accumulator. The saturation logic will substitute a "limited" data value having maximum magnitude and the same sign as the source accumulator.                                                                                                                                                                                     |

|                         | In case saturation occurs when performing a move instruction (MOV or PUSH) from one of the accumulators (AxH, AxL, BxL or BxH) through the XDB, the value of the accumulator is not changed. Only the value transferred over the XDB is limited to a full-scale, 16-bit positive (0x7FFF for AxH or BxH; 0xFFFF for AxL or BxL) or negative (0x8000 for AxH or BxH; 0x0000 for AxL or BxL) value. Limiting will be correctly performed even if the transfer to the XDB does not immediately follow the accumulator overflow. When an accumulator is swapped by the SWAP instruction, limitation will be correctly performed                                       |

Amer

# 12 AT75C DSP Subsystem

when the value is transferred to the XDB. The saturation in move instructions can be disabled by the SAT bit in the register ST0. When limiting occurs, the L flag in ST0 is set. Refer to "Status Registers" on page 23 for more details.

The LIM instruction activates saturation on a 36-bit Ax-accumulator. When there is an overflow from the high portion of an Ax-accumulator to the extension bits and a LIM instruction is executed, the accumulator is limited to a full-scale, 32-bit positive (0 X 7FFFFFF) or negative (0 X 800000) value. Limiting will be correctly performed when the value is operated on by the LIM instruction. The LIM instruction can use the same accumulator for both source and destination or it can use one source Ax-accumulator, which will not change, and transfer the limited result into the other Ax-accumulator. For more details, refer to the LIM instruction in "Instruction Set" on page 31. When limiting occurs, the L flag in ST0 is set. The SAT bit in ST0 has no effect on this instruction. Refer to "Status Registers" on page 23 for more details.

**Swapping the** Accumulators The Ax-accumulators can be swapped with the Bx-accumulators in a single cycle. It is possible to swap two 36-bit registers or all four 36-bits registers. Swapping is also enabled between a specific Ax-accumulator into one of the Bx-accumulators, and in the same cycle, from that Bx-accumulator into the other Ax-accumulator. Similarly, swapping is enabled between a specific Bx-accumulator into one of the Ax-accumulators, and in the same cycle, from that Ax-accumulator into the other Bx-accumulator. For a summary of the 14 swap options and other details, refer to the SWAP instruction in "Instruction Set" on page 31.

> Note that during interrupt context switching, the A1 and B1 accumulators are automatically swapped. For more details, refer to "Interrupt Context Switching" on page 27.

## Data Address Arithmetic Unit (DAAU)

The DAAU performs all address storage and effective address calculations necessary to address data operands in data and program memories and supports the software stack pointer. In addition, it supports latching of the modified register in maximum/minimum operations (see "Maximum/Minimum Operations" on page 9) and loop counter operations in conjunction with the MODR instruction (see "Instruction Set" on page 31) and the R flag (see "Status Registers" on page 23). This unit operates in parallel with other core resources to minimize address generation overhead. The DAAU performs two types of arithmetics: linear and modulo. The DAAU contains six 16-bit address registers (R0, R3 and R4, R5, also referred to as Rn) for indirect addressing, two 16-bit configuration registers (CFGI and CFGJ) for modulo and increment/decrement step control and a base register (RB) for supporting index addressing. In addition, it contains a 16-bit stack pointer register (SP), alternative bank registers (R0B, R1B, R4B, CFGIB) supported by an individual bank exchange and a 16-bit minimum-maximum pointer latching register (MIXP, see "Maximum/Minimum Operations" on page 9). The Rn and configuration registers are divided into two groups for simultaneous addressing over XAB and YAB (or PAB): R0, R3 with CFGI, and R4, R5 with CFGJ. Registers from both groups, in addition to RB and SP, can be used for both XAB and YAB (or PAB) for instructions that use only one address register. In addition, in these instructions the X-RAM and Y-RAM can be viewed as a single continuous data memory space.

The R0, R1, R2, R3, R4, R5, CFGI, CFGJ, SP, RB and MIXP registers may be read from or written to by the XDB as 16-bit operands, and thus can serve as general-purpose registers.

Address Modification The DAAU can generate two 16-bit addresses every instruction cycle, which can be post-modified by two modifiers: linear and modulo. The address modifiers allow the creation of data structures in memory for circular buffers, delay lines, FIFOs, another pointer to the software stack, etc. The Rn registers can also be used, in addition to the block-repeat nesting, as loop counters in conjunction with the MODR instruction (see "Instruction Set" on page 31) and the R flag of ST0 (see "Status Registers" on page 23). Address modification is performed using 16-bit (modulo 65,536) 2's complement linear arithmetic. The range of values of the registers can be considered as signed (from - 32,768 to +32,767) or unsigned (from 0 to +65,535). This is also true for the data space memory map. Index addressing capability is also available. For details, see "Index Modifier".

## **Configuration Registers**

| CFGI          |    |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                                                           |                                                     |                                                          |                                                  |  |

|---------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------|--------------------------------------------------|--|

| 15            | 14 | 13                                                                                                                                                                                                                                                                                                                                                                                    | 12                                                                 | 11                                                                                                        | 10                                                  | 9                                                        | 8                                                |  |

|               |    |                                                                                                                                                                                                                                                                                                                                                                                       | N                                                                  | IODI                                                                                                      |                                                     |                                                          |                                                  |  |

| 7             | 6  | 5                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                  | 3<br>STEPI                                                                                                | 2                                                   | 1                                                        | 0                                                |  |

| FGJ           | -  |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |                                                                                                           |                                                     |                                                          |                                                  |  |

| 15            | 14 | 13                                                                                                                                                                                                                                                                                                                                                                                    | 12                                                                 | 11                                                                                                        | 10                                                  | 9                                                        | 8                                                |  |

|               |    |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    | ODJ                                                                                                       |                                                     |                                                          |                                                  |  |

| 7             | 6  | 5                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                  | 3<br>STEPJ                                                                                                | 2                                                   | 1                                                        | 0                                                |  |

| /lodulo Modif |    | 7-bit step<br>included in<br>and STEP<br>CFGJ, resp                                                                                                                                                                                                                                                                                                                                   | (from -64 to +(<br>the relevant in<br>J are stored a<br>pectively. | nted or post-decr<br>63). The selections<br>structions (see "<br>as the seven LS<br>ic units can updation | on of linear mo<br>Conventions" o<br>Bs of the conf | odifier type (one<br>n page 34). Ste<br>iguration regist | e out of four)<br>p values STEF<br>ters, CFGI an |  |

|               |    | groups within one instruction cycle. They are capable of performing modulo calculations of up to 2 <sup>9</sup> . Each register can be set independently to be affected or unaffected by the modulo calculation using the six Mn status bits in the ST2 register. Modulo setting values MODI and MODJ are stored in nine MSBs of configuration registers CFGI and CFGJ, respectively. |                                                                    |                                                                                                           |                                                     |                                                          |                                                  |  |

|               |    | For proper modulo calculation, the following constraints must be satisfied ( $M = modulo$ factor; $q = STEPx$ , +1 or -1).                                                                                                                                                                                                                                                            |                                                                    |                                                                                                           |                                                     |                                                          |                                                  |  |

|               |    | <ol> <li>Rn should be initiated with a number whose p LSBs are less than M, where p is<br/>the minimal integer that satisfies 2<sup>p</sup> ≤ M.</li> </ol>                                                                                                                                                                                                                           |                                                                    |                                                                                                           |                                                     |                                                          |                                                  |  |

|               |    | <ol> <li>The constraints when the modulo M to the power of 2 (full modulo operation):</li> <li>a. The lower boundary (base address) must have zeros in at least the k LSBs, where k is the minimal integer that satisfies 2<sup>k</sup> ≥ M-1.</li> </ol>                                                                                                                             |                                                                    |                                                                                                           |                                                     |                                                          |                                                  |  |

|               |    | b. MODx (x denotes I or J) must be loaded with M -  q .                                                                                                                                                                                                                                                                                                                               |                                                                    |                                                                                                           |                                                     |                                                          |                                                  |  |

|               |    | c. $M \ge q$<br>3. The constraints when the modulo M is not a power of 2:                                                                                                                                                                                                                                                                                                             |                                                                    |                                                                                                           |                                                     |                                                          |                                                  |  |

|               |    | <ol> <li>The constraints when the modulo M is not a power of 2:</li> <li>a. The lower boundary (base address) must have zeros in at least the k LSBs, where k is the minimal integer that satisfies 2<sup>k</sup> ≥ M -  q .</li> </ol>                                                                                                                                               |                                                                    |                                                                                                           |                                                     |                                                          |                                                  |  |

|               |    |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    | or J) must be lo                                                                                          |                                                     |                                                          |                                                  |  |

|               |    |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    | ,<br>ger multiple of q                                                                                    |                                                     |                                                          |                                                  |  |

|               |    | d. Rn :                                                                                                                                                                                                                                                                                                                                                                               | -                                                                  | ated with a num                                                                                           |                                                     | • •                                                      | nultiple of  q  o                                |  |

|               |    |                                                                                                                                                                                                                                                                                                                                                                                       | denotes the abs                                                    | olute value of q.                                                                                         |                                                     |                                                          |                                                  |  |

|               |    | The modu<br>follows:                                                                                                                                                                                                                                                                                                                                                                  | lo modifier op                                                     | eration, a post-r                                                                                         | modification of                                     | the Rn registe                                           | r, is defined a                                  |  |

|               |    | Rn <- 0 in                                                                                                                                                                                                                                                                                                                                                                            | k LSB; if Rn is                                                    | equal to MODx i                                                                                           | n k LSB and q                                       | ≥ 0,                                                     |                                                  |  |

|                | Rn <- MODx in k LSB; if Rn is equal to 0 in k LSB and q < 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Rn (k LSBs) <- Rn+q (k LSBs); Otherwise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                | When $M =  q $ (i.e., MODx = 0), modulo operation is:<br>Rn <- Rn.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | <ul> <li>Notes: 1. R0 ≥ R3 can only work with STEPI and MODI, while R4 • R5 can work only with STEPJ and MODJ.</li> <li>2. The modulo operation can work for modulo values greater than 512 when the M -  STEPx  ≥ 511 and constraints 3a, 3b, 3c and 3d are met.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                | Examples:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | <ol> <li>M = 7 with STEPx = 1 (or +1 selected in instruction), MODx = 7 - 1 = 6, Rn =<br/>0x0010 (hexa). The sequence of Rn values will be:<br/>0x0010,0x0011,0x0012,0x0013,0x0014,0x0015,0x0016,0x0010,0x0011,</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | <ol> <li>M = 8 with STEPx = 2, MODx = 8 - 2 = 6, Rn = 0x0010. The sequence of Rn values will be: 0x0010,0x0012,0x0014,0x0016,0x0010,0x0012,</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                | <ol> <li>M = 9 with STEPx = -3, MODx = 9 -  -3  = 6, Rn = 0x0016. The sequence of Rn values will be:<br/>0x0016,0x0013,0x0010,0x0016,0x0013,</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                | <ol> <li>M = 8 with STEPx = 3, (2<sup>3</sup> = 8 - full modulo support), MODx = 8 - 3 = 5, Rn = 0x0010.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | The sequence of Rn values will be:<br>0x0010,0x0013,0x0016,0x0011,0x0014,0x0017,0x0012,0x0015,0x0010,0x0013                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Index Modifier | The OakDSPCore has short and long index addressing modes. The base register is RB, one of the DAAU registers. In the short index addressing mode, the base register, together with a 7-bit signed short immediate value (-64 to +63) embedded in the instruction opcode, is used to point to a data memory location in a single cycle. In the long index addressing mode, the base register, together with a signed 16-bit offset, given as the second word of the instruction, is used to access the memory in two cycles. Unlike the linear and modulo addressing modes, in both index addressing modes, address premodification is performed prior to accessing the memory. The base register is unaffected. Indexed addition, subtraction, compare, AND, OR, XOR and move from/into the pointed data memory location can be performed in either one or two cycles, using the short or long mode, respectively. |

|                | The base register can be used as an array pointer or in conjunction with the stack<br>pointer (SP) register. When the stack is used for transferring routine parameters, initial-<br>izing the base register by the SP value enables quick access to routine parameters<br>transferred using the stack. The index addressing mode is useful for supporting C-<br>compiler.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | The RB register is part of the global register set and can be used as a general-purpose register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Software Stack | The OakDSPCore contains a software stack, pointed to by a dedicated 16-bit register, the stack pointer (SP). The SP contains the address of the top value in the stack; there-<br>fore, it points to the last value pushed onto the stack. The stack is filled from high memory address to low memory address. A POP instruction performs a post-increment; a PUSH instruction performs a pre-decrement. The Program Counter (PC) is automati-<br>cally pushed to the stack whenever a subroutine call or an interrupt occurs and popped back on return from subroutine or interrupt. Other values can be pushed and popped                                                                                                                                                                                                                                                                                        |

# 16 AT75C DSP Subsystem

using the PUSH and POP instructions. The top of stack can be read without affecting SP using a dedicated MOV instruction.

The software stack can reside anywhere in the data space (X-RAM and Y-RAM) and can be accessed by any other pointer (R0 to R5 and RB).

The software stack is useful for supporting the C-compiler. The stack can be used for transferring routine parameters (e.g., C-automatic variables). Thus, after initializing the base register (RB) by the SP value, the routine parameters can be referenced by the index mode with the MOV, ADD, SUB, CMP, AND, OR and XOR instructions. Another support for transfer of routine parameters is the RETS instruction, which returns from a subroutine and updates the SP by a short immediate value.

The SP register is part of the global register set. Refer to "Programming Model and Registers" on page 23.

Alternative Bank of Registers The DAAU contains an alternative bank of four registers: R0B, R1B, R4B, CFGIB. For each of the R0/R0B, R1/R1B, R4/R4B or CFGI/CFGIB, only one register is accessible at a time. The selection between the current or the alternative register is controlled by a special BANKE instruction, which exchanges (swaps) the contents between the current register with the alternative bank register.

The bank exchanging is selected individually, meaning that the BANKE instruction includes a list of registers to be exchanged in a single cycle. For the four registers there are 15 different options. Refer to BANKE instruction in "Instruction Set" on page 31.

The individual selectivity of the bank registers contributes to flexibility of the bank registers. The user can decide where each of the alternative registers will be utilized in interrupts, routines, etc.

### Program Control Unit (PCU)

The Program Control Unit (PCU) performs instruction fetch, instruction decoding, exception handling, hardware loop control, wait state support and on-chip emulation support. In addition, it controls the internal program memory protection. Refer to "Program Memory".

The PCU contains the Repeat/Block-repeat unit and two 16-bit directly accessible registers: the Program Counter (PC) and the Loop Counter (LC).

The PCU selects and/or calculates the next address from several possible sources:

- the incremented PC in sequential program flow

- jump address in branch or call operations

- short PC-relative address of seven bits in relative branch or call operations

- start address and exit address of hardware loops

- interrupts vector handling

- user write to PC or the top value on the stack, pointed to by the SP register upon returning from subroutines and interrupts

The PCU also writes the PC to the top of stack in subroutines and interrupts.

The PC always contains the address of the next instruction.

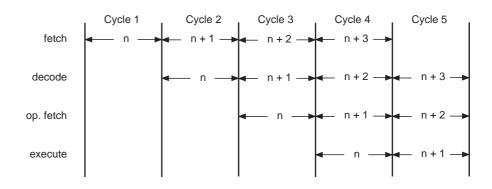

For more information on the pipeline method, refer to "Pipeline Method" on page 140.

#### Repeat and Block-repeat Unit

The Repeat/Block-repeat unit performs the hardware-loop calculations and controls execution without overhead (other than the one-time execution of set up instructions REP or BKREP for initialization of repeat or block-repeat mechanism, respectively). Four nested levels of block-repeat can be performed and the REP instruction can be performed inside each one of the these levels.

The number of repetitions can be a fixed value embedded in the instruction code or a value transferred from one of the processor's 16-bit registers. This option supports calculating the number of repetitions in run-time.

For the repeat operation, the unit contains an internal 16-bit repeat counter (REPC) for repeating a single-word instruction from 1 to 65536 repetitions. REPC counter is readable by the programmer.

In block-repeat operation, the last and first addresses of a loop are stored in 16-bit dedicated registers. A 16-bit dedicated counter, LC, counts the number of loop repetitions (1 - 65536). In case of nested block-repeats, it saves these values in internal registers. The LC of each level can be accessed by the user; the start-address and end-address registers and the internal shadow registers cannot be accessed as registers by the programmer. An indication of the block-repeat nesting level is a read-only block-repeat nesting counter (BC2, BC1, BC0) in the internal configuration register (ICR). See also "Internal Configuration Register" on page 29. The 16-bit block-repeat loop counter (LC) is one of the global registers. The LC register can be used as an index inside the blockrepeat loop or for determining the value of the block-repeat counter when a jump out of the block-repeat loop occurs.

The single instruction repeat can reside in each of the block-repeat levels. Both the repeat and the block-repeat mechanisms are interruptible. For details, on specific limitations, refer to REP and BKREP instructions in "Instruction Set" on page 31.

A BREAK instruction can be used for stopping each of the four nested levels of a blockrepeat. Refer to the BREAK instruction in "Instruction Set" on page 31.

The in-loop (LP) bit in the ICR is set when a block-repeat is executed and reset upon normal completion of the outer block-repeat loop. When the user resets this bit, it stops the execution of all four levels of block-repeat. For more details on the LP bit, refer to "Internal Configuration Register" on page 29. If the LP bit is cleared in the current block-repeat loop, the processor is no longer in any of the block loop levels (BC2, BC1, BC0 bits in ICR register are cleared). Therefore, when the last address is reached there are no jumps to the first address of the loop, the counter is not decremented and the processor continues to the sequential instruction. An exception is when LP is cleared at one of the last three addresses of the block-repeat. In these cases the effect of clearing LP takes place only in the next loop. An instruction that reads ICR and starts at last address of the outer block-repeat loop results in the LP bit equal to zero when the last repetition of this outer loop is reached.

The LC register may also serve as a 16-bit general-purpose register for temporary storage.

# Memory Spaces and Organization

Two independent memory spaces are available: the data space (X-RAM and Y-RAM) and the program space.

**Program Memory**

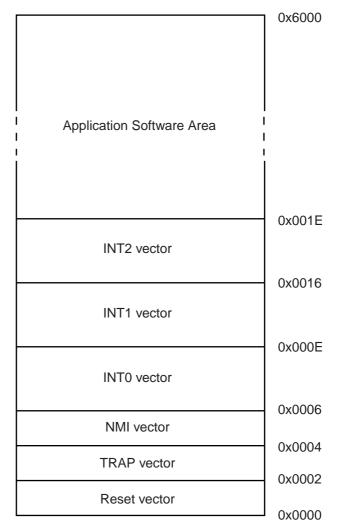

Addresses 0x0000 to 0x0016 are used as interrupt vectors for Reset, TRAP (software interrupt with option for hardware activation), NMI (non-maskable interrupt) and three maskable interrupts (INT0, INT1, INT2). The RESET, TRAP and NMI vectors have been separated by two locations so that branch instructions can be accommodated in those locations if desired. The maskable interrupts have been separated by eight locations so that branch instructions, can be accommodated in those that branch instructions, or small and fast interrupt service routines, can be accommodated in those dated in those locations.

The program memory addresses are generated by the PCU.

Figure 7. Program Memory Diagram

Note that in the AT75C the interrupts have been affected as shown in Table 2.

| Interrupt   | Affectation                                           |

|-------------|-------------------------------------------------------|

| TRAP        | Used in conjunction with the OCEM for debug purposes  |

| NMI         | Not used                                              |

| INTerrupt 0 | Indicates that the dual-port mailbox requires service |

| INTerrupt 1 | Indicates that the codec interface requires service   |

| INTerrupt 2 | Not used                                              |

**Table 2.** Affectation of the Interrupt Request Lines

#### **Data Memory**

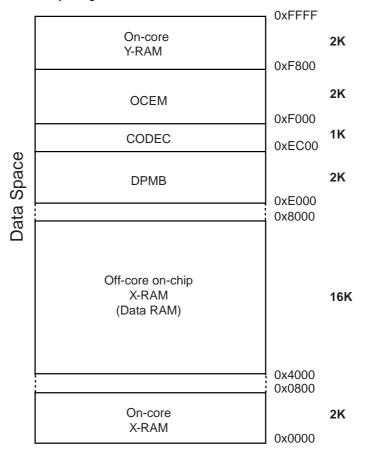

The data space is divided as follows:

- a Y-data space for the on-core Y-RAM (2K x 16)

- an X-data space for the on-core X-RAM (2K x 16)

- an additional X-data space for an on-chip but off-core X-RAM (16K x 16)

- the dual-port mailbox (refer to "Dual-port Mailbox" on page 152 and following sections)

- memory-mapped I/Os for peripherals connection

The on-core Y-RAM space and the on-core X-RAM space are mapped to allow a continuous data space. The data space partition allows expansion of the X-RAM, which has been grown off-core with an additional 16K x 16 block. This off-core block is used as general-purpose working memory and can be accessed with no wait state cycles. The dual-port mailbox is also seen in the X-data space.

Memory-mapped I/Os are used to connect to on-chip peripherals (OCEM, codec interface). They are seen by the OakDSPCore in the X-data space. Refer to Figure 8.

# AT75C DSP Subsystem

Figure 8. Data Memory Diagram

| Memory Addressing<br>Modes   | There are five data memory addressing modes.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Short Direct Addressing Mode | Eight bits embedded in the instruction opcode as LSBs plus eight bits from status register ST1 as MSB (see "Status Registers" on page 23) compose the 16-bit address to the data memory. The pages are thus of 256 words each. For example, page 0 corresponds to addresses 0 to 255 in X-RAM, page 1 from 250 to 511 in X-RAM and page 255 from - 256 to -1 in Y-RAM. Any memory location in the 64K-word data space can be directly accessed in a single cycle. |